在數位電路的世界中,edge detection circuit如同敏銳的哨兵,時刻監視著訊號每一次跳動。當訊號從低電平(0)瞬間躍升至高電平(1),或從高電平(1)驟然降至低電平(0)時,這些電路能迅速捕捉到這些關鍵時刻,並產生短暫的脈衝信號作為回應。這種精確的偵測能力對於時序控制、資料同步和事件觸發等應用相當重要。

方法一:使用邏輯閘

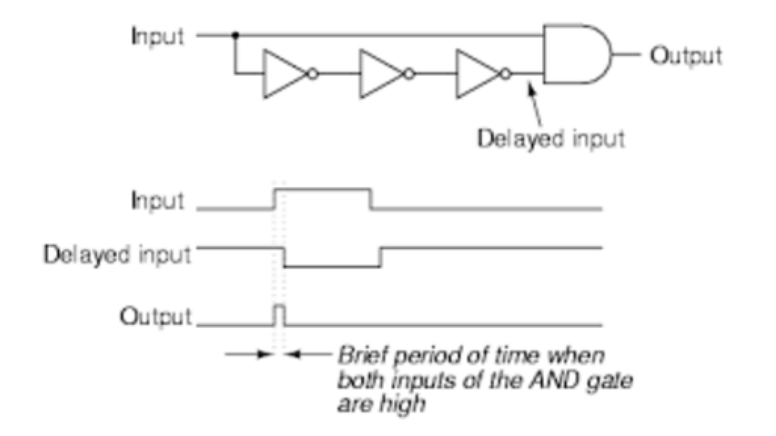

要偵測輸入訊號的正緣,就把自己和延遲反向後的自己(前面兩顆inv是用來延遲輸入訊號的,也可以說讓此刻的訊號訊號和前一刻訊號的反向和比較)and起來就好

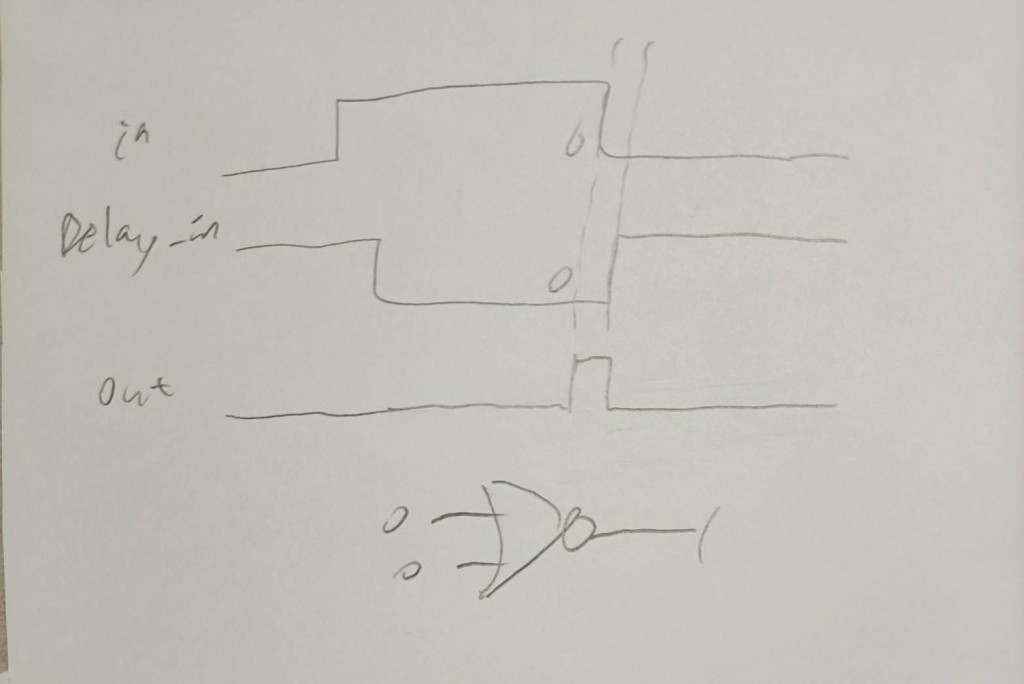

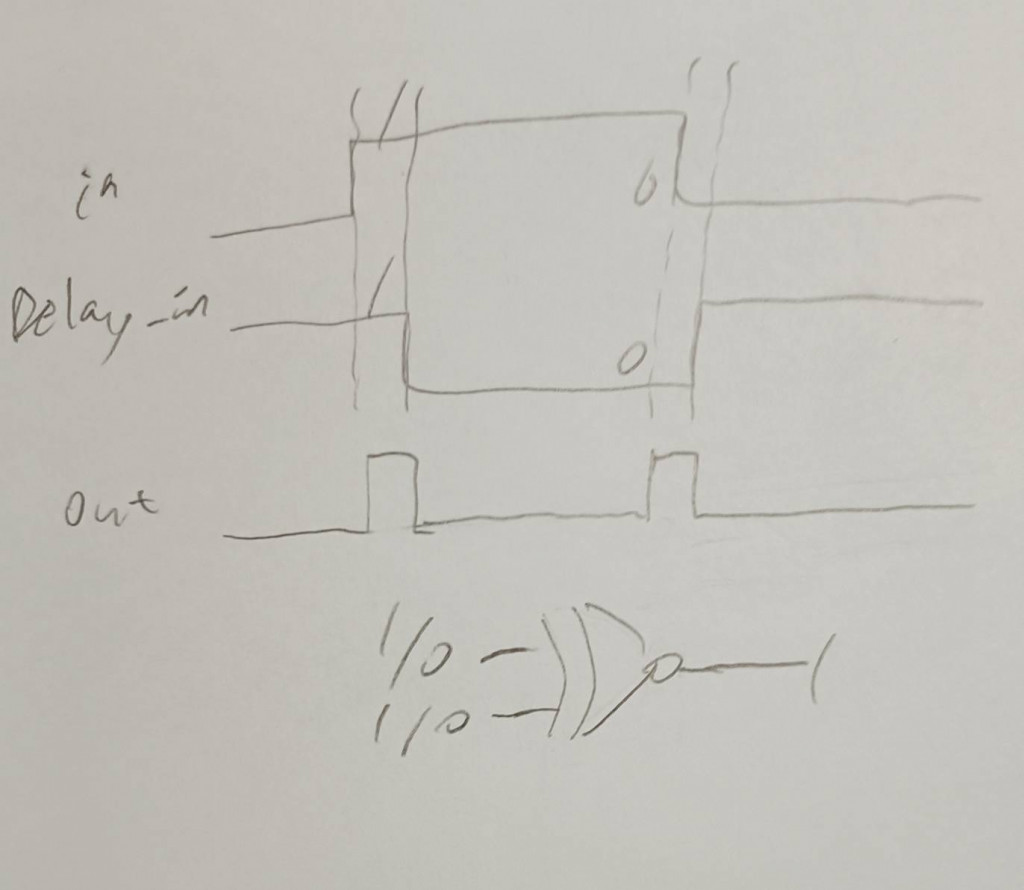

如果要偵負緣,就把and換成換成nor就好

要同時偵側正負緣,就用xnor

方法二:使用 D Flip-Flop + 邏輯閘

把上圖的buffer改成DFF也可以達到相同的效果

方法三:使用opamp

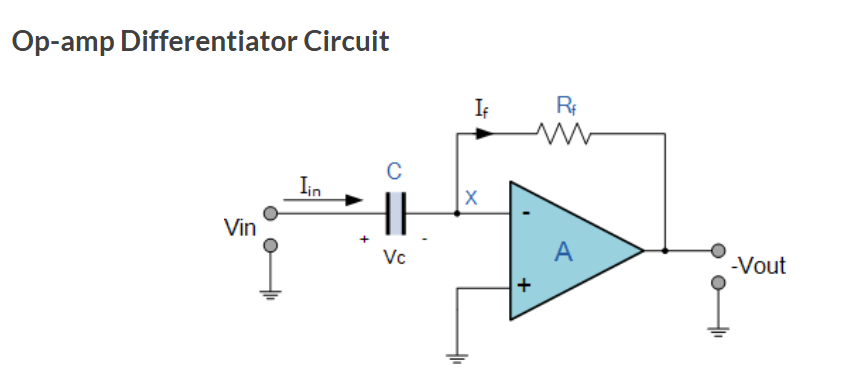

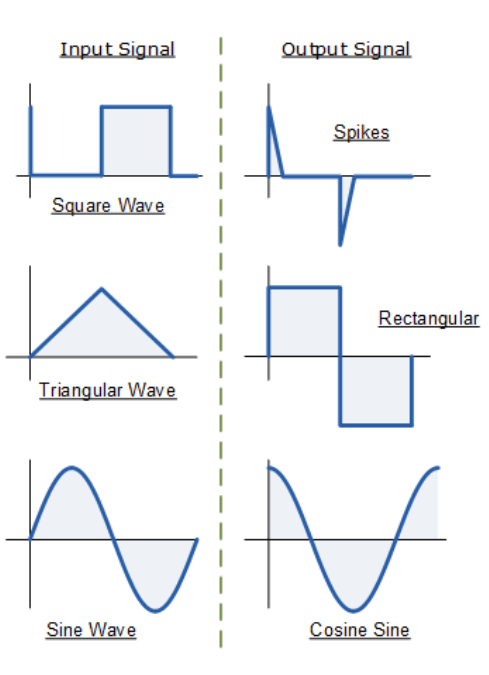

類比的話,用一個微分器就搞定了

但有以下缺點

由於電路在高頻下的增益特性,可能導致不穩定,甚至引發振盪,而且輸入端的電容使電路對隨機噪聲非常敏感,任何存在於輸入端的噪聲或諧波都可能被放大,影響輸出信號的質量。為了減少這些缺點,通常會在設計中引入適當的頻率補償、濾波器或限制輸入信號的頻率範圍,以確保電路的穩定性和性能。

參考資料:

https://electronics.stackexchange.com/questions/270089/falling-and-rasing-edge-detector

https://www.electronics-tutorials.ws/opamp/opamp_7.html